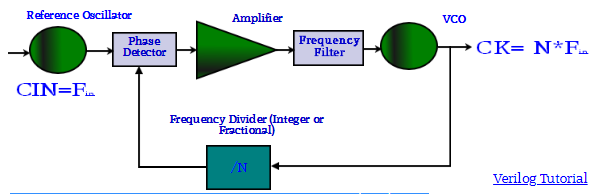

PLL’s or phase locked loop

low speed clocks, phase synchronization of clocks, separate valuable signal information from noise and also used to demodulate amplitude and frequency modulated signals.Follow this section for PLL’s in ASIC, FPGA configuration.

A Very accurate and stable Reference Oscillator, Phase Detector, Frequency Divider -

PLL classification

Analog PLL :-

Analog components -

Digital PLL (DPLL) :-

Digital components -

Analog components -

All digital PLL (ADPLL)

Digital components -

Follow this section for PLL’s for ASIC, FPGA configuration.

Interview Questions. ASIC, FPGA, Digital Fundamentals

5 Steps required to build a functional FPGA load (valid for most EDA flows)

How to implement a Integrated Clock Gating (ICG) cell from vendor library.

CMOS Digital Integrated Circuit design for VLSI.

Hope you liked! this page. Don't forgot to access relevant previous and next sections with links below.